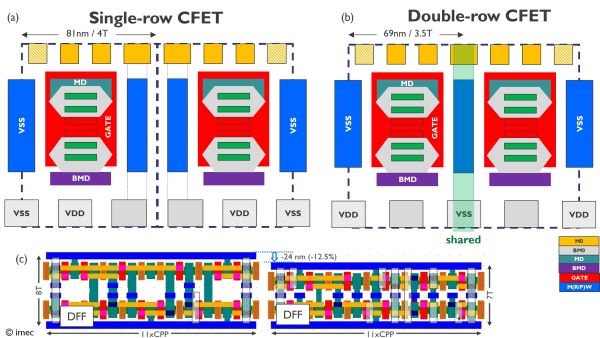

The main benefits of this double-row CFET architecture are process simplification, and significant logic and SRAM cell area reduction according to imec’s design-technology co-optimisation (DTCO) study. The new architecture will allow standard cell heights to be reduced from 4 to 3.5T, compared to conventional single-row CFETs.

The semiconductor industry is making considerable progress in fabricating (monolithic) CFET devices that are expected to succeed gate-all-around nanosheets (NSHs) in the logic technology roadmap.

The stacking of n- and pFET devices promises benefits in power, performance, and area (PPA) when combined with backside technologies for power delivery and signal routing. At the circuit level, however, several options are still open for integrating the CFETs into a standard cell to sustain or enhance the expected PPA benefits.

According to imec, especially challenging is the middle-of-line (MOL) connectivity, i.e., the interconnects that connect source/drain and gate contacts to the first metal lines (at back- and frontside) and ensure top-to-bottom connectivity for both power and signal.

From a DTCO study comparing standard cell architectures, imec was able to show that the double-row CFET offers the most optimal trade-off between manufacturability and area efficiency for A7 logic nodes.

This new architecture starts from a base cell in which one side of the CFET is optimised for power connections – including a power rail (VSS) to deliver power from the backside to the top device and a direct backside connection for the bottom device. The other side is optimised for signal connections by providing a middle routing wall (MRW) for top-to-bottom connectivity.

The double-row CFET standard cell (with two rows of stacked devices) is then formed by mirroring two base cells, which share the same MRW for signal connectivity (see below).

Geert Hellings, Program Director DTCO at imec said, “Our DTCO study shows that one shared MRW for every 3.7 FET is sufficient to build logic and SRAM cells. This allows us to further reduce standard cell heights from 4 to 3.5T, compared to ‘classical’ single-row CFETs. This translates into a significant area reduction of 15 percent for SRAM cells.

“Compared to SRAMs built with, e.g., A14 NSH technology, double-row CFET-based SRAMs enable more than 40 percent area shrinkage, providing a further scaling path for SRAMs.”

The double-row CFET also leads to process simplification because of the shared MRW trench between two rows of CFET devices. This eliminates the need for an extra high-aspect-ratio via to connect the top and bottom devices, if necessary, reducing MOL processing complexity and cost.

“Since the 7nm technology node, standard cell optimisation through DTCO is providing an increasingly large share of node-to-node density increase, in addition to conventional device scaling,” added Hellings. “For our DTCO study on CFET architectures, we started from the process capabilities envisioned in future CFET fabs to ensure industry-relevant process flows. In addition, we validate our virtual fab concept with technology proofs-of-concept performed in imec’s 300mm cleanroom. This combination of virtual fab and real pilot line activities is a crucial step in advancing our roadmaps.”

As such, also at IEDM, imec will be experimentally demonstrating a key building block of this double-row CFET architecture: a functional monolithic CFET with direct backside contact to the source/drain of the bottom pMOS device.

This was realised through EUV backside patterning that ensured dense backside power and signal wiring and tight overlay (<3nm accuracy) between the source/drain created from the frontside, backside contact, and subsequent backside metal layers.