Monolithic chips have been the workhorses behind decades of technological advancement. But just as the industrial revolution saw workhorses replaced with more efficient and powerful machinery, the technology industry is on the cusp of a similar revolution.

Multi-die and chiplet-based designs - which integrate multiple specialised dies in a single package or stack integrated circuits vertically - stand to deliver far greater performance and flexibility than monolithic chips, capable of supporting the insatiable processing demands of high-performance computing (HPC) and AI-driven workloads.

But pursuing these advanced chip designs has required the deepest of pockets and most advanced R&D capabilities.

That is, until now.

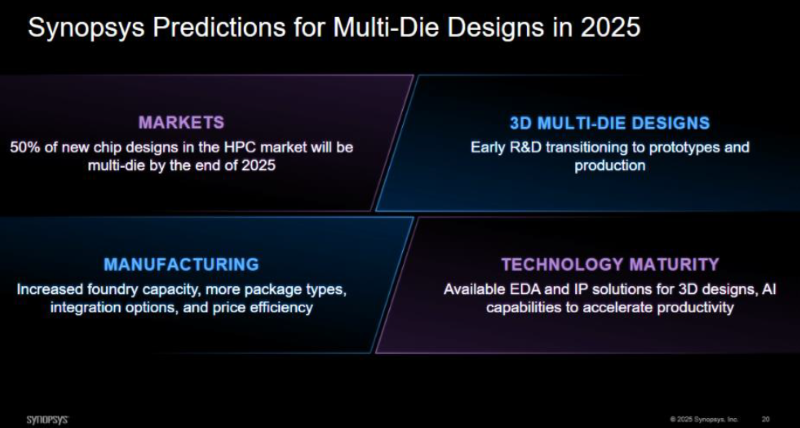

Multi-die technologies, tools, flows, and IP have matured rapidly. Engineering expertise has evolved. And foundry capacity continues to expand. With this in mind, we predict 50% of new HPC chip designs will be 2.5D or 3D multi-die in 2025.

Foundries preparing for wave of 2.5D and 3D multi-die designs

It takes more than R&D to bring 2.5D and 3D multi-die designs to market. It also requires high-bandwidth, low-latency interconnects (3DIO), advanced manufacturing processes with sufficient capacity, and sophisticated design tools and IP.

Open industry standards like UCIe (Universal Chiplet Interconnect Express) continue to mature, helping simplify and strengthen the connectivity between heterogeneous chiplets while reducing risk and accelerating design cycles. The increased adoption of UCIe for HPC, AI, data centre, and edge applications is driving significant demand for 2.5D and 3D multi-die designs.

In addition to the maturation and proliferation of advanced interconnects, foundries are preparing for the oncoming wave of 2.5D and 3D multi-die designs. This includes new manufacturing processes that offer denser bumps and higher performance. Additional package, interposer, and integration options provide cost and architectural flexibility. And expanded production capacity means more designs and prototypes can be brought to market.

Advanced design tools and IP

Developing these cutting-edge chips would not be possible without the most advanced design solutions, and Synopsys remains at the forefront of 2.5D and 3D multi-die innovation. The company has developed comprehensive and scalable multi-die solutions, including design automation tools and IP that enable:

- Early architecture exploration

- Rapid software development and system validation

- Efficient die/package co-design

- Robust die-to-die and chip-to-chip connectivity

- Improved manufacturing and reliability

In particular, our 3DIC Compiler is currently the industry’s only unified exploration-to-signoff platform for 2.5D and 3D multi-die designs. Certified by all major foundries, it supports feasibility exploration, multi-die partitioning, and foundry technology selection for prototyping and floor planning. This enables analysis-driven design implementation (including advanced packaging and die-to-die routing) with golden signoff verification.

3DIC Compiler also integrates with 3DSO.ai, Synopsys’ AI-driven system analysis and optimisation solution. The integrated solutions help maximise system performance and quality of results for thermal integrity, signal integrity, and power network design.

Synopsys can also offer high performance, low latency, low power, and the smallest area die-to-die IP solutions, including UCIe and proprietary controllers, physical layer devices (PHYs), and verification IP. The UCIe-based IP is compliant with the latest UCIe specification, and the proprietary die-to-die IP delivers 40Gbps performance, maximum die-edge and power efficiency, low latency, and support for standard and advanced packaging technologies.

Customer adoption and foundry capacity continue to increase. And 3DIO standards continue to mature.

For these reasons and more, we believe at least half of new HPC chip designs will be 2.5D or 3D multi-die in 2025.

Authors details: Shekhar Kapoor is a senior director of product line management for the Synopsys EDA Group, while Michael Posner is a VP of marketing for the Synopsys Solutions Group